This is a 64 channels logic analyzer with 100 MHz samplerate for the Parallella platform. All source code is available at GitHub. In the sampler directory is the Linux driver, the network server and the Java client program. See the GitHub commit changes for details, but the main VHDL code for the logic analyzer is in this file.

The usage of the Java program is similar to some oscilloscopes. With the Run/Stop button you can sample the input signals continuously. If no trigger is set, it show the live data, with maximum update rate. If a trigger is set, it waits for the trigger condition with a holdoff of half the sample buffer and the other half of the buffer after the trigger condition. In single mode, it triggers only once, then stops.

With the cursor buttons you can set two cursors. The status bar at the bottom of the window shows the delta time between the two cursors.

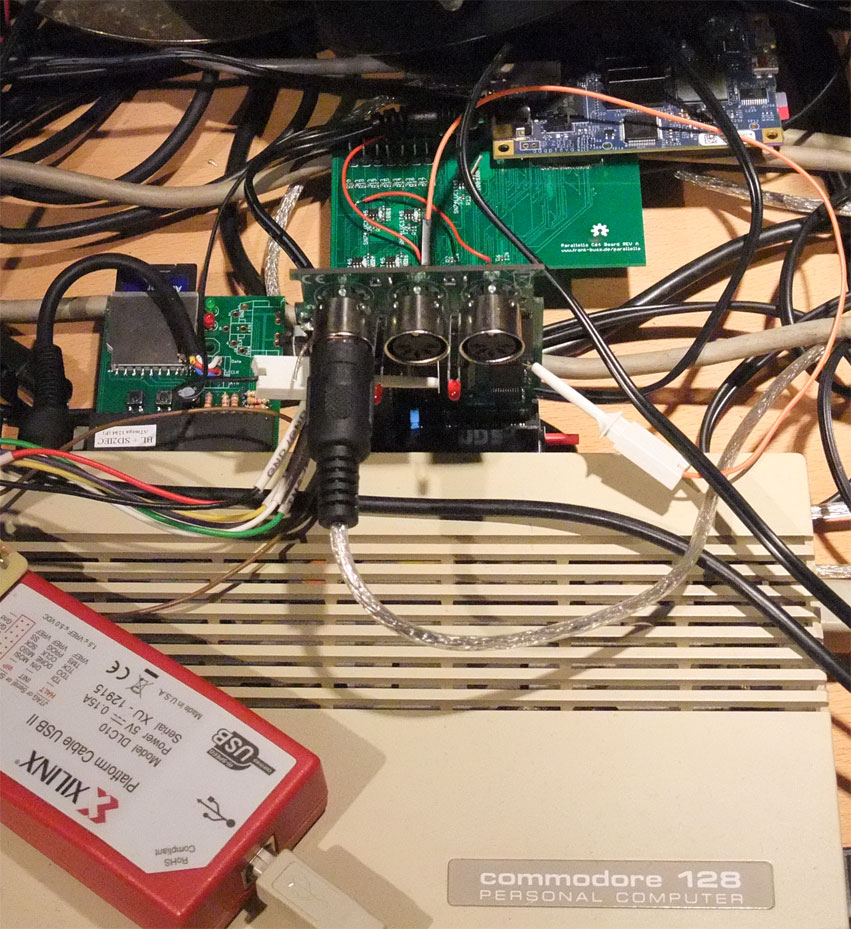

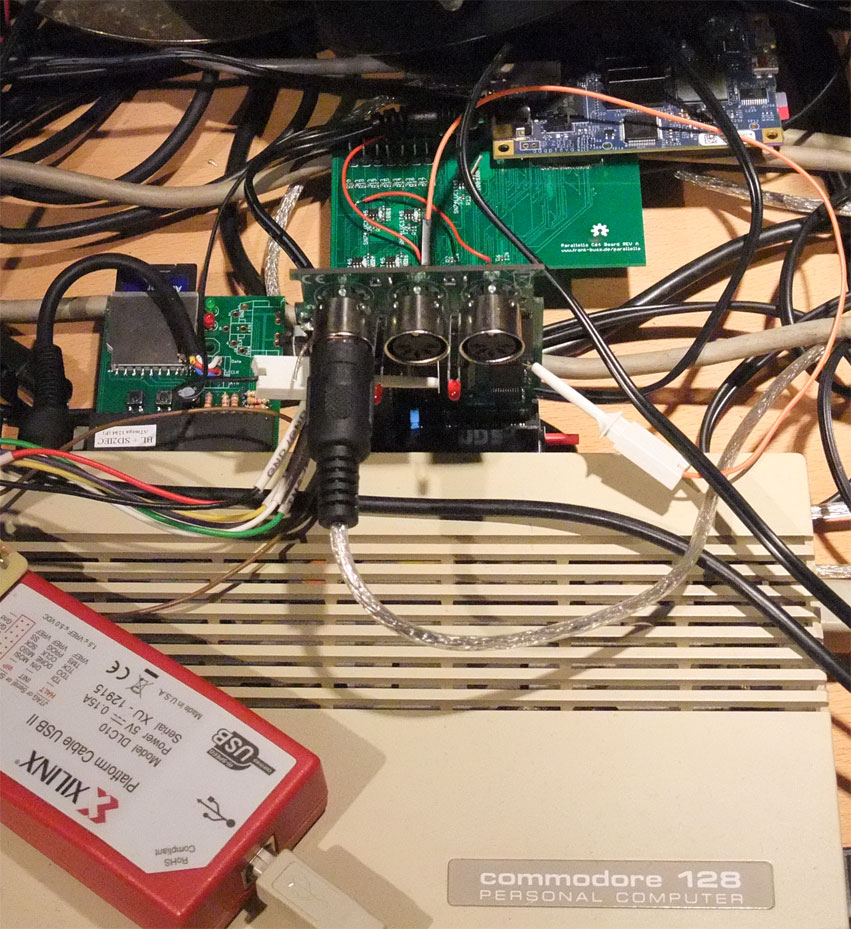

As a test project, I created an adapter to sample the expansion port signals on a C64 and C128 (see schematic and board in PDF format, and the Eagle files. I was lazy and used the Eagle auto router). The adapter uses voltage level translators with a direction pin, which can be controlled from the Parallella to use it as a cartridge emulator, too. For my test setup I change two pins, because I needed to sample some more pins from my cartridge. Then I used my Kerberos MIDI cartridge with an cartridge extender and the adapter with the Parallella board on a C128:

This short test program runs on the C128 and demonstrates the logic analyzer:

7000 78 SEI 7001 A9 01 LDA #$01 7003 8D 00 04 STA $0400 7006 4C 03 70 JMP $7003

You can see how it looks like in the beginning of this video:

After stopping the sampling, I measured the time until the address is stable after rising edge of the S02 clock. Then I used the "single" mode to trigger on reset and looked at the chipselect of my flash when the C64 KERNAL reads the cartridge ID.